6564 - Radiant and All Nexus: How to reserve certain pin or pins without any logic in the design?

Description:

In planning for a design, ports and pins are should be set earlier prior to adding logic in the design, and reserving a pins without any logic is part of that hardware abstraction.

Solution:

Procedure to reserved certain pin or pins.

1. Go to DCE (Device Constraint Editor).

2. Look for the graphical package view of all the pins.

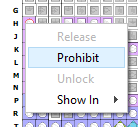

3. Right click on the desired pin.

4. Then choose "Prohibit".

5. Save the changes.

6. The constraint will be added to PDC.

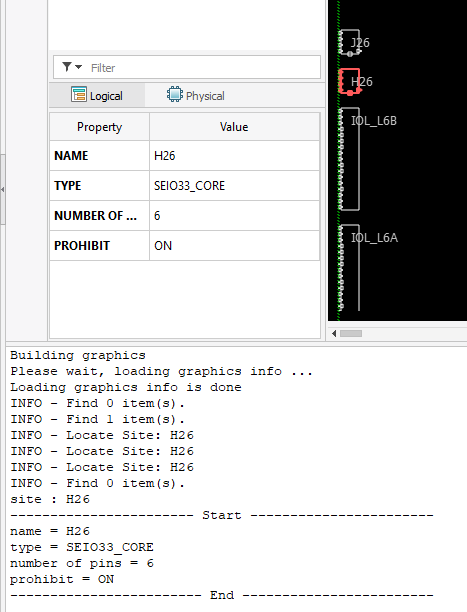

PDC file content: ldc_prohibit -site H26

PDC file content: ldc_prohibit -site H26

The user can also opt to directly write on the PDC by using the "ldc_prohibit" constraint.

Usage: ldc_prohibit –site site OR ldc_prohibit –region region

Options: site: site name, region: region name

Then, check the signal/pad report under PAR to check if the reserved pin is accepted.

Pinout by Pin Number:

+----------+-----------------------+------------+--------------+-----------------+---------------

| Pin/Bank | Pin Info | Preference | Buffer Type | Site | Dual Function |

+----------+-----------------------+------------+--------------+-----------------+---------------

H26/7 | Prohibited/Reserved | PROHIBITED | | PL6A | EIO

The information is also added on the "Attribute" tab of DCE and the Physical Designer pin info.

The information is also added on the "Attribute" tab of DCE and the Physical Designer pin info.

Related Articles

6994 - Lattice Radiant: How do I use the RGB pins on iCE40UltraPlus as GPIO?

The SB_IO_OD primitive is only available for the iCECube2 SW, you will have to use BB_OD as this is the equivalent primitive for the opendrain buffer in Radiant. Note that for Radiant, BB_OD is automatically mapped in the netlist/design whenever you ...7688 - [All Nexus] Why Lattice Radiant tool shows Error <71241012> The clock port [clock_name] is assigned to a non-clock pin ?

This error appears when you are assigning a clock port to a non-clock pin. To resolve this, you can force Radiant tool to use this attribute in the .pdc file: ldc_set_attribute {USE_PRIMARY=FALSE} [get_nets {clock_name}_c] Example: ldc_set_attribute ...7010 - Radiant 2023.2 and below: How to create a design-specific BSDL for Nexus devices?

You can create an application-specific BSDL file using Radiant Deployment Tool. However, the tool only supports specific BSDL files that target non-volatile memory (using *.jed file), which is inapplicable for Nexus devices that target SRAM (*.bit).7242 - Radiant versions 2023.1 and newer: Why is there a MAP DRC update on 2023.1 and newer versions of Radiant that blocks the compilation of designs with all configuration ports disabled?

In the Nexus series of devices, if you intend to utilize JTAG ports as GPIO by de-asserting JTAG_EN, then there must be another dual-use pin (e.g. I2C) that remains in “persisted” mode (e.g. I2C must stay as I2C and not become a GPIO). Keeping I2C ...6575 - Lattice Nexus devices using Reveal: no output from LVDS IP

Description: While debugging your Radiant design using Reveal, users may observe that there is no output from their LVDS IP. Solution: When Reveal is inserted in Nexus devices, on certain designs, the GSR net gets assigned to a reset signal that may ...